- 您好,歡迎來(lái)到商城眾網(wǎng)!

- [請(qǐng)登錄/注冊(cè)]

- 幫助中心

功耗優(yōu)化多過(guò)性能 ARM Cortex-A73評(píng)測(cè)

盡管現(xiàn)在智能手機(jī)和平板之類的設(shè)備現(xiàn)已對(duì)極致功能沒(méi)有了太多的訴求,但VR又成了下一個(gè)著力點(diǎn),近來(lái)ARM就在Computex 2016上公布了可以說(shuō)是為VR設(shè)備的沉浸式體驗(yàn)預(yù)備的Cortex-A73新架構(gòu),均對(duì)VR的功能和顯現(xiàn)需要做好了預(yù)備。

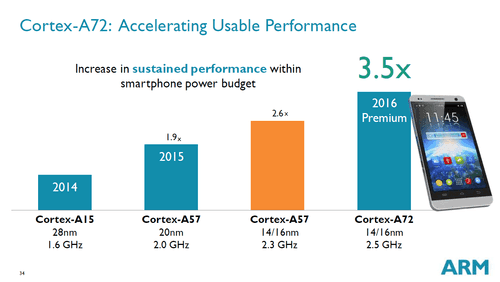

回顧一下前任A72,作為big.LITTLE架構(gòu)里的大核在今年的主流市場(chǎng)得到了廣泛應(yīng)用,驍龍650里有兩個(gè),驍龍652里有四個(gè),麒麟950/955里有四個(gè),聯(lián)發(fā)科Helio X20/X25里有兩個(gè),當(dāng)然考慮到各自的不同定位,工作頻率及制程工藝上的選擇都各有不同;從產(chǎn)品分布可以看出,今年的Cortex-A72并不如前任Cortex-A57那樣在高端市場(chǎng)吃香(驍龍810、Exynos 7420),三星用了半自主架構(gòu),而高通則徹底回到自主架構(gòu)。

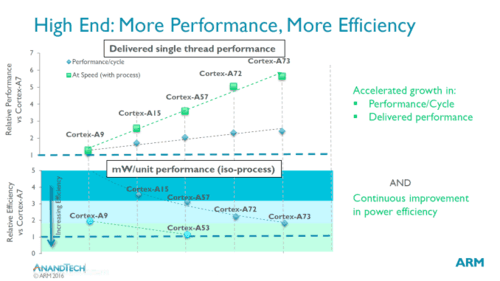

拋開(kāi)那顆著名的壽命極長(zhǎng)、高能效比的Cortex-A7不說(shuō),Cortex-A9是對(duì)于ARM來(lái)說(shuō)極為重要的里程碑,采用該架構(gòu)的平臺(tái)——諸如蘋果A5、三星Exynos 4210/4412、德儀OMAP 4430/4460都證明了A9的成功。

之后便是毀譽(yù)參半的Cortex-A15,性能相比之前突飛猛進(jìn)的同時(shí)帶來(lái)了不小的功耗和發(fā)熱問(wèn)題,比如Exynos 5250/5410都受其影響,再想想當(dāng)年的核彈Tegra 4什么的……

而看到這一問(wèn)題的ARM也在隨后推出了著名的big.LITTLE架構(gòu),隨之誕生了全球首款真八核Exynos 5422,以及麒麟920等平臺(tái)。

隨著Cortex-A57的登場(chǎng),ARM陣營(yíng)正式邁入ARMv8 64位指令集時(shí)代,當(dāng)然這也是蘋果A7的功勞,與Cortex-A53結(jié)合的大小核架構(gòu)成為了隨后的主流,其中出現(xiàn)了4大4小、2大4小、不同頻率的兩組4小各種組合方式,并流傳至今;其中有人歡喜有人愁,三星靠Exynos 7420成功奪得眼球,而驍龍810則因?yàn)榘l(fā)熱問(wèn)題成為了一代尷尬的旗艦。

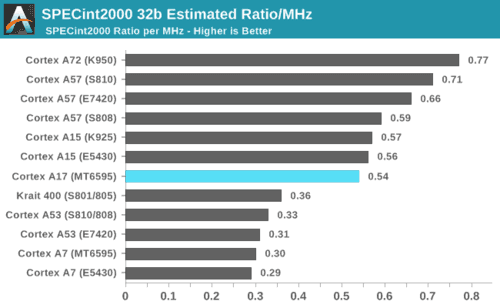

在這些主流微架構(gòu)之外,還有2013年7月公布的Cortex-A12以及2014年2月公布的Cortex-A17,短命和不受待見(jiàn)沒(méi)讓其成為主流,只有MT6595這樣極少的平臺(tái)采用。

而此次的A73并非是簡(jiǎn)單的A72升級(jí),這還要從ARM的家族劃分說(shuō)起,A15、A57、A72屬于Austin家族(來(lái)源于ARM位于美國(guó)德州奧斯汀的設(shè)計(jì)中心),而A5、A7、A53則屬于Cambridge家族(名字來(lái)源于ARM總部英國(guó)劍橋),A12、A17以及剛剛公布的A73屬于Sophia家族(名字來(lái)源于歐洲最大科技園區(qū)索菲亞(002572,股吧),也就是ARM法國(guó)CPU設(shè)計(jì)中心所在地)。

雖然命名上Cortex-A73看似是A72的升級(jí),但是從技術(shù)層面講,它其實(shí)是A17的進(jìn)化版本,整體微架構(gòu)、流水線、寬度設(shè)計(jì)都與之類似,反而和A72差別很大,并且,A73也沒(méi)有保留A72的三發(fā)射,而是采用了與之前的Sophia家族微架構(gòu)相同的雙發(fā)射。而ARM此次的宣傳顯然也是側(cè)重能效而非性能,對(duì)于前兩代動(dòng)輒5W甚至10W的峰值功耗來(lái)說(shuō),ARM期待Cortex-A73能夠長(zhǎng)效的保持高性能,而不是因?yàn)槎虝焊哳l運(yùn)行后發(fā)熱降頻,換句話說(shuō),要持久…

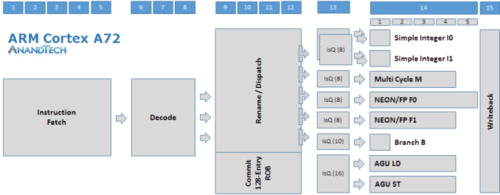

對(duì)比一下A73與A72的流水線圖,你就能發(fā)現(xiàn)設(shè)計(jì)思路上的顯著不同。Cortex-A72采用了15級(jí)以上的亂序流水線設(shè)計(jì)、128位預(yù)取指令、3發(fā)射解碼、每個(gè)時(shí)鐘周期分配最多5個(gè)微操作、滿足最多7個(gè)發(fā)射隊(duì)列進(jìn)入8個(gè)執(zhí)行流水線。

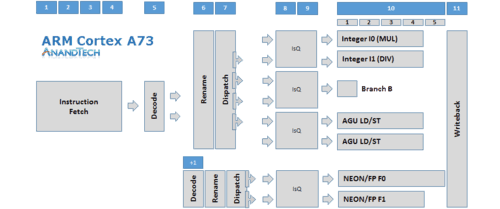

而A73的設(shè)計(jì)頗似A17,流水線深度較A72有所減少,預(yù)取階段從A72的5級(jí)減少為4級(jí),進(jìn)入浮點(diǎn)流水線的微操作還經(jīng)過(guò)一個(gè)額外的取指階段,整個(gè)流水線只有11~12級(jí)。

由此可以看出A73的設(shè)計(jì)基于跟A17相同的邏輯,通過(guò)優(yōu)化流水線、資源和接口來(lái)在可實(shí)現(xiàn)的最小功耗水平上獲取最高的性能。ARM也表示他們還特別進(jìn)行了32位/64位狀態(tài)下的平衡優(yōu)化。

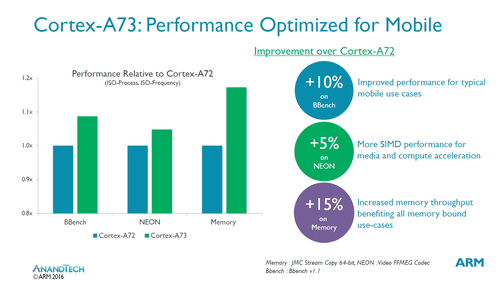

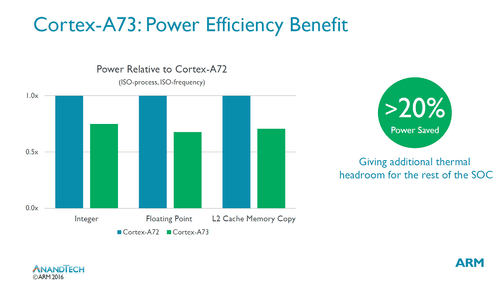

而更被看重的性能方面,整數(shù)應(yīng)用當(dāng)中A73有25%的功耗降低,浮點(diǎn)和二級(jí)緩存應(yīng)用當(dāng)中有30%左右的降低,ARM也表示在相同的頻率下,A73整體相對(duì)于A72有著20%的功耗降低。

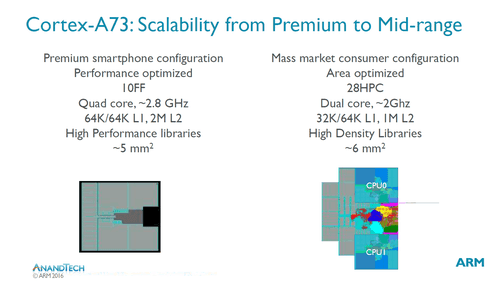

10nm制程讓A73的尺寸在相同性能下比A72小25%,因此雙核A73的尺寸基本跟四核A53相同,特別是在如今眾多采用4+4 A53設(shè)計(jì)的處理器性能表現(xiàn)并不搶眼的情況下,這一組合有望被2xA73+4xA53的設(shè)計(jì)替代,在核數(shù)減少單線程性能大幅提升的同時(shí)保持相同的芯片面積。

(轉(zhuǎn)載至網(wǎng)絡(luò),僅作為相關(guān)資訊的傳播普及目的,如果原作者發(fā)現(xiàn)內(nèi)容的使用不符合本人意愿,請(qǐng)聯(lián)系本站作者或客服,將第一時(shí)間刪除處理)

- 推薦商品評(píng)測(cè)

- 最新商品評(píng)測(cè)

- 月榜

- 1游戲Cpu怎么誰(shuí)?i7-6700K、i5-6600K大戰(zhàn)AMD 8核FX 8370

- 24898元!Intel i7-6770HQ骷髏峽谷迷你機(jī)評(píng)測(cè):功能巔峰

- 3兩塊SSD組RAID 0 速度不升反降?

- 4Intel Broadwell-E十核心CPU評(píng)測(cè)

- 5《黑手黨3》顯卡測(cè)驗(yàn):4K千萬(wàn)別碰 TITAN X也跪

- 6Intel 22核心CPU對(duì)比評(píng)測(cè)

- 7英特爾至強(qiáng)E7-8890 v4處理器性能測(cè)試

- 8ARM Cortex-A73評(píng)測(cè) 功耗優(yōu)化多過(guò)性能

- 9Intel七代酷睿將至!如今買四代還值嗎?

- 10千兆板載網(wǎng)卡實(shí)測(cè)PK:高通Killer E2500游戲神器 虐Intel

促銷活動(dòng) 優(yōu)惠券 更多>

登錄后,通過(guò)商城眾網(wǎng)去官方商城,購(gòu)買拿返利,得積分

下單付款后十分鐘內(nèi),您可以在商城眾網(wǎng)的個(gè)人中心查看訂單信息

- 登錄商城眾網(wǎng)

- 去合作商家購(gòu)買

- 回商城眾網(wǎng)拿返利積分